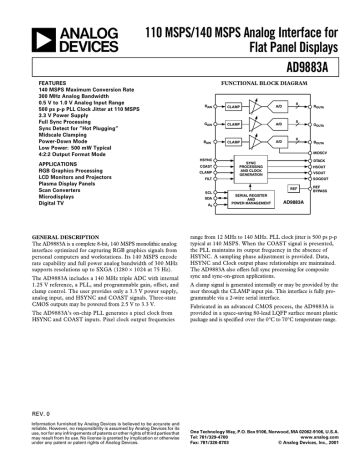

advertisement

AD9883A

PIN FUNCTION DESCRIPTIONS

Pin Name Function

OUTPUTS

HSOUT

VSOUT

SOGOUT

Horizontal Sync Output

A reconstructed and phase-aligned version of the Hsync input. Both the polarity and duration of this output can be programmed via serial bus registers. By maintaining alignment with DATACK, and Data, data timing with respect to horizontal sync can always be determined.

Vertical Sync Output

A reconstructed and phase-aligned version of the video Vsync. The polarity of this output can be controlled via a serial bus bit. The placement and duration in all modes is set by the graphics transmitter.

Sync-On-Green Slicer Output

This pin outputs either the signal from the Sync-on-Green slicer comparator or an unprocessed but delayed version of the Hsync input. See the Sync Processing Block Diagram (Figure 12) to view how this pin is connected.

(Note: Besides slicing off SOG, the output from this pin gets no other additional processing on the AD9883A.

Vsync separation is performed via the sync separator.)

SERIAL PORT

(Two-Wire)

SDA

SCL

A0

Serial Port Data I/O

Serial Port Data Clock

Serial Port Address Input 1

For a full description of the two-wire serial register and how it works, refer to the Two-Wire Serial Control Port section.

DATA OUTPUTS

RED Data Output, RED Channel

GREEN

BLUE

Data Output, GREEN Channel

Data Output, BLUE Channel

The main data outputs. Bit 7 is the MSB. The delay from pixel sampling time to output is fixed. When the sampling time is changed by adjusting the PHASE register, the output timing is shifted as well. The DATACK and HSOUT outputs are also moved, so the timing relationship among the signals is maintained. For exact timing information, refer to Figures 7 and 8.

DATA CLOCK OUTPUT

DATACK Data Output Clock

This is the main clock output signal used to strobe the output data and HSOUT into external logic. It is produced by the internal clock generator and is synchronous with the internal pixel sampling clock. When the sampling time is changed by adjusting the PHASE register, the output timing is shifted as well. The Data, DATACK, and HSOUT outputs are all moved, so the timing relationship among the signals is maintained.

INPUTS

R

AIN

G

AIN

B

AIN

Analog Input for RED Channel

Analog Input for GREEN Channel

Analog Input for BLUE Channel

High-impedance inputs that accept the RED, GREEN, and BLUE channel graphics signals, respectively. (The three channels are identical, and can be used for any colors, but colors are assigned for convenient reference.) They accommodate input signals ranging from 0.5 V to 1.0 V full scale. Signals should be ac-coupled to these pins to support clamp operation.

HSYNC

VSYNC

Horizontal Sync Input

This input receives a logic signal that establishes the horizontal timing reference and provides the frequency reference for pixel clock generation. The logic sense of this pin is controlled by serial register 0Eh Bit 6 (Hsync

Polarity). Only the leading edge of Hsync is active, the trailing edge is ignored. When Hsync Polarity = 0, the falling edge of Hsync is used. When Hsync Polarity = 1, the rising edge is active. The input includes a Schmitt trigger for noise immunity, with a nominal input threshold of 1.5 V.

Vertical Sync Input

This is the input for vertical sync.

SOGIN Sync-on-Green Input

This input is provided to assist with processing signals with embedded sync, typically on the GREEN channel. The pin is connected to a high-speed comparator with an internally generated threshold. The threshold level can be programmed in 10 mV steps to any voltage between 10 mV and 330 mV above the negative peak of the input signal. The default voltage threshold is 150 mV. When connected to an ac-coupled graphics signal with embedded sync, it will produce a noninverting digital output on SOGOUT. (This is usually a composite sync signal, containing both vertical and horizontal sync information that must be separated before passing the horizontal sync signal to Hsync.) When not used, this input should be left unconnected. For more details on this function and how it should be configured, refer to the Syncon-Green section.

–6– REV. 0

advertisement

* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Related manuals

advertisement

Table of contents

- 2 Specifications

- 5 Pinout

- 24 Package Drawings

- 4 Ordering Guide

- 1 Features

- 1 Applications

- 1 Product Description

- 4 Absolute Maximum Ratings

- 1 Functional Block Diagram

- 6 Pin Function Description

- 4 EXPLANATION OF TEST LEVELS

- 6 OUTPUTS

- 6 DATA OUTPUTS

- 6 DATA CLOCK OUTPUT

- 6 INPUTS

- 7 POWER SUPPLY

- 7 DESIGN GUIDE

- 15 TWO-WIRE SERIAL CONTROL REGISTER DETAIL

- 15 CHIP IDENTIFICATION

- 15 PLL DIVIDER CONTROL

- 16 MODE CONTROL 1

- 16 INPUT GAIN

- 20 WIRE SERIAL CONTROL PORT

- 22 PCB LAYOUT RECOMMENDATIONS

- 8 Diagrams

- 8 Analog Input Interface Circuit

- 9 Typical Clamp Configuration

- 10 PLL Loop Filter Detail

- 11 Output Timing

- 12 4:2:2 Mode (For YUV Only)

- 20 Serial Port Read/Write Timing

- 21 Sync Processing Block Diagram