advertisement

Chapter 2 4S648/4S648N BIOS Setup

2.5 Advanced Chipset Features

This section allows you to configure the system based features of the installed chipset. This chipset manages bus speeds and access to system memory resources, such as

DRAM and external cache. It also coordinates communications of the PCI bus. It must be stated that these items should never be altered. The default settings are set up to provide the best operating conditions for your system. The time you might need to make any changes would be if you discover that data is lost while using your system.

Phoenix - AwardBIOS CMOS Setup Utility

Advanced Chipset Features

Item Help

DRAM Clock/Timing Control

DRAM Timing Control x DRAM CAS Latency x RAS Active Time x RAS Precharge Time x RAS to CAS Delay (tRCD)

DRAM Addr/Cmd Rate

AGP & P2P Bridge Control

AGP Aperture Size

Graphic Window WR Combin

Prefetch Caching

System BIOS Cacheable

Video RAM Cacheable

Memory Hole at 15M-16M

Press Enter

By SPD

2.5T

6T

3T

3T

Press Enter

64MB

Disabled

Disabled

Enabled

Enabled

Disabled

←→↑↓ : Move Enter:Select +/-/PU/PD:Value F10:Save ESC:Exit F1:General Help

F5:Previous Values F6:Fail-Safe Defaults F7:Optimized Defaults

2-40

Chapter 2 4S648/4S648N BIOS Setup

DRAM Clock/Timing Control: Press <Enter> to reveal the following submenu.

DRAM iming Control

Use this item to select the DRAM Clock/Timing mode.

The Choices:

By SPD: DRAM Timing is by Serial Presence Detect (SPD) which is located on the memory module itself.

Manual: DRAM Timing is set manually with the options following this item below.

X DRAM CAS Latency

This item is to set CAS (Column Access Stroke) Latency time.

The Choices: Auto; 1.5; 2; 2.5;

X RAS Active ,Time

This item is to set Active to Precharge Delay cycle.

The Choices: Auto; 7; 6; 5

X DRAM RAS# to CAS# Delay (tRCD)

This item is to set the DRAM RAS (Row Access Stroke) to CAS

(Column Access Stroke) Delay cycle.

The Choices: Auto; 3; 2

X DRAM RAS# Precharge

This item is to set the DRAM RAS Precharge cycle.

The Choices: Auto; 3; 2

DRAM Addr/Cmd Rate

This item is to set the DRAM Addr/Command rate.

The Choices: Auto; 1T; 2T

2-41

Chapter 2 4S648/4S648N BIOS Setup

AGP & P2P BBridge Control: Press <Enter> to reveal the following submenu.

AGP Aperture Size

Select the size of the Accelerated Graphic Port(AGP) aperture .

The aperture is a portion of the PCI memory address range dedicated for graphics memory address space. Host cycle that hit the aperture range are forwarded to the AGP without any translation.

The Choices: 128MB(default); 64MB,;32MB; 16MB; 8MB;

4MB; 256MB

Graphic Window WR Combin

Use this item to enable/disable the Graphic Window Write

Combin function.

The choices: Enabled; Disabled

Prefetch Caching

This item is to enable/disable the Prefetch Caching function.

The Choices: Enabled , Disabled.

System BIOS Cacheable

This item is to enable/disable the System BIOS Cacheable function.

Video RAM Cacheable

Enabled: Enable Video RAM Cacheable.

Disabled :Disable Video RAM Cacheable.

Memory Hole At 15-16M

In order to improve performace, certain space in memory can be reserved for ISA cards. This memory must be mapped into the memory's space below 16MB.

The Choices: Disabled; Enabled.

2-42

advertisement

Related manuals

advertisement

Table of contents

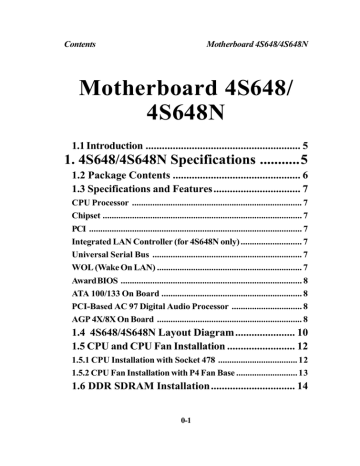

- 5 1.1 Introduction

- 5 1. 4S648/4S648N Specifications

- 6 1.2 Package Contents

- 7 1.3 Specifications and Features

- 7 CPU Processor

- 7 Chipset

- 7 Integrated LAN Controller (for 4S648N only)

- 7 Universal Serial Bus

- 7 WOL (Wake On LAN)

- 8 Award BIOS

- 8 ATA 100/133 On Board

- 8 PCI-Based AC 97 Digital Audio Processor

- 8 AGP 4X/8X On Board

- 10 1.4 4S648/4S648N Layout Diagram

- 12 1.5 CPU and CPU Fan Installation

- 12 1.5.1 CPU Installation with Socket

- 13 1.5.2 CPU Fan Installation with P4 Fan Base

- 14 1.6 DDR SDRAM Installation

- 40 2.5 Advanced Chipset Features

- 43 2.6 Integrated Peripherals

- 48 2.7 Power Management Setup

- 51 2.8 PnP/PCI Configurations

- 54 2.9 PC Health Status

- 55 2.10 Frequency/Voltage Control

- 57 2.11 Load Fail-Safe Defaults

- 58 2.12 Load Optimized Defaults

- 59 2.13 Set Supervisor / User Password

- 60 2.14 Save & Exit Setup

- 61 2.15 Exit Without Saving

- 62 3. Drivers & Utilities

- 62 3.1 Auto-run Menu

- 64 3.2 Install Acceleration Graphics Driver

- 65 3.3 Installing SiS IDE PCI Driver

- 66 3.4 Install PCI LAN Driver (for 4S648N)

- 68 3.4 Installing Audio Driver

- 68 3.4.1 Installing 6-channel Driver

- 68 3.4.2 Verifying 6-channel Driver

- 70 3.5 Installing USB 2.0 Driver